# Section 23. CodeGuard<sup>TM</sup> Security

## **HIGHLIGHTS**

This section of the manual contains the following major topics:

| 23.1  | Code Protection Overview                                   | 23-2  |

|-------|------------------------------------------------------------|-------|

| 23.2  | Device Specific Code Protection Features                   | 23-3  |

| 23.3  | Program Memory Organization                                | 23-4  |

| 23.4  | Data RAM Organization                                      |       |

| 23.5  | Control Registers                                          | 23-5  |

| 23.6  | The Boot Segment (BS)                                      | 23-6  |

| 23.7  | The Secure Segment                                         | 23-20 |

| 23.8  | The General Segment                                        | 23-25 |

| 23.9  | The Reset, Trap and Interrupt Service Routine Vector Space | 23-28 |

| 23.10 | Definition of Security Privileges                          | 23-28 |

| 23.11 | Rules Concerning Program Flow                              | 23-30 |

| 23.12 | Rules Concerning Interrupts                                | 23-33 |

| 23.13 | Rules for Accessing RAM Data                               | 23-34 |

| 23.14 | Security Features and Device Operational Mode              | 23-35 |

| 23.15 | Typical Procedures for Boot Loading a Device               | 23-36 |

| 23.16 | Typical Installation of Third Party Protected Algorithm    | 23-37 |

| 23.17 | Design Tips                                                | 23-38 |

| 23.18 | Related Application Notes                                  | 23-39 |

| 23.19 | Revision History                                           | 23-40 |

|       |                                                            |       |

## 23.1 CODE PROTECTION OVERVIEW

Microchip's CodeGuard™ Security enables multiple parties to securely share resources (memory, interrupts and peripherals) on a single chip. Intellectual Property (IP) vendors, Original Design/Original Equipment Manufacturers (ODM/OEM) and Value-Added Resellers (VAR) now have an opportunity to reap the following benefits using these on-chip code protection features:

- · System cost reduction

- · Component reduction and associated benefits to inventory management

- · Decreased risk of losing IP to unqualified partners

- Increased security during code distribution and Flash memory update

The on-chip program Flash memory in a dsPIC33F device can be organized into three code space segments. Each of these segments has an implied security privilege level and system function.

- The Boot Segment (BS) has the highest security privilege level. It has greater access to the other segments. The Boot Segment is intended for secure boot loader and device update functions.

- 2. The Secure Segment (SS) is the next highest security privilege. This segment is designed for storing proprietary algorithms from algorithm vendors.

- The General Segment (GS) has the lowest security privilege. This segment is designed for the end user system code.

Segments of user data RAM space of the device can be allocated as secure RAM, which are directly associated with the Boot or Secure segments.

Any operation of the system that potentially allows exposure of the code or data contents is restricted, based on the segment from which the operation originated, or the segment to which the operation targets.

Restricted operations include:

- Programming, Erase or Verify Operations

- Reads or Writes of Code Space

- · Reads or Writes of Protected Data Space

- Code Flow Change into a Secure Segment from outside the segment

- Interrupt Vectors into a Secure Segment

Configuration bits are provided to enable access to the Secure Segments and their parameters. These bits allow configuration of both the sizes and restrictions of the program Flash memory, and RAM segments.

# CodeGuard<sup>™</sup> Security

## 23.2 DEVICE SPECIFIC CODE PROTECTION FEATURES

Two different subsets of CodeGuard Security features are available on dsPIC33F devices.

On devices with smaller memory sizes, program memory can be allocated to Boot Segment and General Segment; however, there is no Secure Segment and no Data RAM protection.

On larger memory devices, memory can be allocated to Boot Segment, Secure Segment and General Segment code space. On these larger memory devices, Data RAM can be allocated to Boot and Secure Segments.

Table 23-1 shows the code protection features that are available. Refer to the specific device data sheet to correlate these features with specific devices or product families.

Table 23-1: Code Protection Features

| Feature                                     | Smaller<br>Memory<br>Devices | Larger<br>Memory<br>Devices |

|---------------------------------------------|------------------------------|-----------------------------|

| Assign Code Space as Boot Segment           | Yes                          | Yes                         |

| Assign Code Space as Secure Segment         | _                            | Yes                         |

| Assign Code Space as General Segment        | Yes                          | Yes                         |

| Assign Data Ram to Boot and Secure Segments |                              | Yes                         |

## 23.3 PROGRAM MEMORY ORGANIZATION

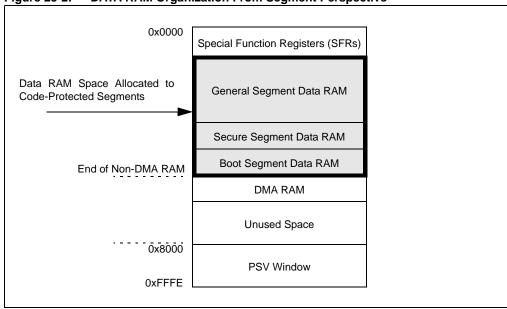

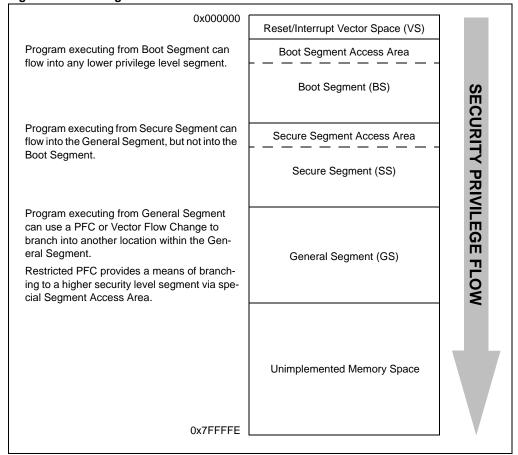

The total user program memory can be allocated into one of the three segments. The size of these different segments is determined by Configuration bits. The relative location of the segments does not change, such that a Boot Segment, if present, occupies the memory area just after the device interrupt vector space. The Secure Segment, if present, occupies the space just after the Boot Segment and the General Segment occupies the space just after the Secure Segment (refer to Figure 23-1).

0x000000 Reset/Interrupt Vector Space (VS) Boot Segment space immediately **Boot Segment Access Area** follows the Reset/Interrupt Vector Space Boot Segment (BS) Secure Segment space immediately Secure Segment Access Area follows the Boot Segment Secure Segment (SS) General Segment space immediately follows the Secure Segment General Segment (GS) Max Internal User Memory Size Unimplemented Memory Space 0x7FFFFE

Figure 23-1: Program Memory Organization From Segment and Privilege Perspective

## 23.4 DATA RAM ORGANIZATION

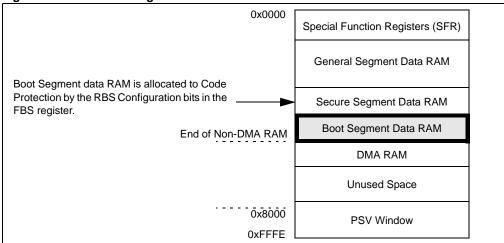

Data RAM memory can also be allocated into code protection segments: Boot, Secure and General. Segment size is primarily specified by Configuration bits. The relative locations of the segments do not change, meaning that a Boot Segment RAM area occupies the memory region at the end of the non-DMA RAM, the Secure Segment RAM occupies the area just before the Boot Segment and the General Segment RAM occupies the remainder of the data RAM space (refer to Figure 23-2).

**Note:** DMA RAM is not present on all dsPIC33F devices. For DMA RAM availability and sizes, refer to the specific device data sheet.

Figure 23-2: DATA RAM Organization From Segment Perspective

## 23.5 CONTROL REGISTERS

Several Configuration and Special Function Registers control the security functions. On basic and intermediate security implementations, some of these registers do not exist. The key registers for supporting the code security features are:

- FBS: Boot Segment Configuration Register Byte

- BSRAM: Boot Segment RAM Special Function Register

- FSS: Secure Segment Configuration Register Byte

- SSRAM: Secure Segment RAM Special Function Register

- FGS: General Segment Configuration Register

- INTTREG: Interrupt Vector and Priority Status Special Function Register

## 23.6 THE BOOT SEGMENT (BS)

The Boot Segment has the highest privilege. The Boot Segment can be small, allowing a simple yet secure boot loader, or it can be large, enabling it to hold a more sophisticated secure operating system.

The Boot Segment can also rewrite its own locations, enabling it to store and update data such as "encryption keys".

## 23.6.1 Allocating the Boot Segment

The existence and size of the Boot Segment are determined by Configuration bits BSS<2:0> (FBS<3:1>). The default option, on an erased non-programmed device, is to exclude the Boot Segment. When implemented, the Boot Segment begins at the end of the interrupt vector space and continues to an address specified by the BSS<2:0> bits.

**Figure 23-3: Boot Segment Memory Allocation** 0x000000 Reset/Interrupt Vector Space (VS) Boot Segment space immediately Boot Segment Access Area follows the Reset/Interrupt Vector Space and continues to an address specified by BSS<2:0>\_ Boot Segment (BS) Secure Segment Access Area Secure Segment (SS) General Segment (GS) Max Internal User Memory Size Unimplemented Memory Space 0x7FFFFE

DS70199B-page 23-6

## 23.6.1.1 BOOT SEGMENT SIZE OPTIONS

Table 23-2 provides an example of Boot Segment size options (in this case, for devices with 64 KB flash memory). The start and end program memory addresses listed are typical. For specific program memory addresses for a given device, refer to the device data sheet.

Table 23-2: Boot Segment Size Example

| BSS2:BSS0 | Security Level | BS Size         | BS Start<br>Address | BS End<br>Address |

|-----------|----------------|-----------------|---------------------|-------------------|

| x11       |                | No Boot Program | n Flash Segment     |                   |

| 110       | Standard       | Small           | 0x000200            | 0x0007FE          |

| 010       | High           | Small           | 0x000200            | 0x0007FE          |

| 101       | Standard       | Medium          | 0x000200            | 0x001FFE          |

| 001       | High           | Medium          | 0x000200            | 0x001FFE          |

| 100       | Standard       | Large           | 0x000200            | 0x003FFE          |

| 000       | High           | Large           | 0x000200            | 0x003FFE          |

#### Register 23-1: FBS: Boot Segment Configuration Register Byte

Lower Third Byte:

| R/P   | R/P  | U | U | R/P  | R/P  | R/P  | R/P   |

|-------|------|---|---|------|------|------|-------|

| RBS1  | RBS0 | R | R | BSS2 | BSS1 | BSS0 | BWRP  |

| bit 7 |      |   |   |      |      |      | bit 0 |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 7-6 RBS<1:0>: Boot Segment RAM Code Protection bits<sup>(1)</sup>

11 = No Boot RAM defined

10 = Boot RAM is 128 Bytes

01 = Boot RAM is 256 Bytes

00 = Boot RAM is 1024 Bytes

bit 5-4 Reserved bits: Programming values will have no effect

bit 3-1 BSS<2:0>: Boot Segment Program Flash Code Protection bits<sup>(2)</sup>

X11 = No Boot program Flash segment

110 = Standard security, Small Boot Segment

010 = High security, Small Boot Segment

101 = Standard security, Medium Boot Segment

001 = High security, Medium Boot Segment

100 = Standard security, Large Boot Segment

000 = High security, Large Boot Segment

bit 0 BWRP: Boot Segment Program Flash Write Protection bit

1 = Boot segment can be written

0 = Boot segment is write-protected

**Note 1:** Not all devices have Boot Segment RAM code protection. For device specific information refer to Table 23-3, Table 23-4 and Table 23-5.

- 2: The exact definitions of Small, Medium, and Large Boot Segment vary from one device to another. For device specific information refer to Table 23-6, Table 23-7 and Table 23-8.

- 3: If a Boot Segment is not needed, the BWRP bit must be programmed as a "1".

DS70199B-page 23-9

Section 23. CodeGuard™ Security

Table 23-3: Data RAM Segment Sizes for Devices with 30 KB RAM

| CONFIGURATION BITS                                                 | RBS<1:0> = 11<br>OR<br>RBS<1:0> = 10 AND RL_BSR = 1 | RBS<1:0> = 10 AND RL_BSR = 0<br>OR<br>RBS<1:0> = 01 AND RL_BSR = 1 | RBS<1:0> = 01 AND RL_BSR = 0<br>OR<br>RBS<1:0> = 00 AND RL_BSR = 1 | RBS<1:0> = 00 AND RL_BSR = 0        |

|--------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|-------------------------------------|

| RSS<1:0> = 11                                                      | GS RAM = 28672 0x0800                               | GS RAM = 28544 0x0800                                              | GS RAM = 28416 0x0800                                              | GS RAM = 27648 0x0800               |

| OR<br>RSS<1:0> = 10 AND RL_SSR = 1                                 |                                                     |                                                                    | BS RAM = 256 0x7700                                                | BS RAM = 1024 0x7400                |

|                                                                    | 0x77FF                                              | BS RAM = 128  0x7780 0x77FF                                        | 0x77FF                                                             | 0x77FF                              |

| RSS<1:0> = 10 AND RL_SSR = 0                                       | GS RAM = 28416 0x0800                               | GS RAM = 28416 0x0800                                              | GS RAM = 28416 0x0800                                              | GS RAM = 27648 0x0800               |

| OR<br>RSS<1:0> = 01 AND RL_SSR = 1                                 | SS RAM = 256 0x7700 0x77FF                          | SS RAM = 128  BS RAM = 128  0x7700 0x7780 0x77FF                   | BS RAM = 256  0x7700  0x77FF                                       | BS RAM = 1024 0x7400 0x77FF         |

|                                                                    | GS RAM = 26624 0x0800                               | GS RAM = 26624 0x0800                                              | GS RAM = 26624 0x0800                                              | GS RAM = 26624 0x0800               |

| RSS<1:0> = 01 AND RL_SSR = 0<br>OR<br>RSS<1:0> = 00 AND RL_SSR = 1 | SS RAM = 2048 0x7000                                | SS RAM = 1920 0x7000                                               | SS RAM = 1792 0x7000                                               | SS RAM = 1024 0x7000 0x7400         |

|                                                                    | 0x77FF                                              | BS RAM = 128                                                       | BS RAM = 256 0x7700 0x77FF                                         | 0x77FF                              |

| RSS<1:0> = 00 AND RL_SSR = 0                                       | GS RAM = 24576<br>SS RAM = 4096 0x6800              | GS RAM = 24576<br>SS RAM = 3968 0x6800                             | GS RAM = 24576<br>SS RAM = 3840 0x6800                             | GS RAM = 24576 0x0800 0x6800 0x6800 |

| Legend: OR = Logical OR AN                                         | 0x77FF                                              | BS RAM = 128                                                       | BS RAM = 256 0x7700 0x77FF                                         | BS RAM = 1024                       |

**Legend:** OR = Logical OR, AND = Logical AND

Table 23-4: Data RAM Segment Sizes for Devices with 16 KB RAM

| CONFIGURATION BITS                                                 | RBS<1:0> = 11<br>OR                    | RBS<1:0> = 10 AND RL_BSR = 0<br>OR     | RBS<1:0> = 01 AND RL_BSR = 0<br>OR     | RBS<1:0> = 00 AND RL_BSR = 0                 |

|--------------------------------------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------|----------------------------------------------|

| CONFIGURATION BITS                                                 | RBS<1:0> = 10 AND RL_BSR = 1           | RBS<1:0> = 01 AND RL_BSR = 1           | RBS<1:0> = 00 AND RL_BSR = 1           | NB3<1.05 = 00 AND NL_B3N = 0                 |

| RSS<1:0> = 11                                                      | GS RAM = 14336 0x0800                  | GS RAM = 14208 0x0800                  | GS RAM = 14080 0x0800                  | GS RAM = 13312 0x0800                        |

| OR<br>RSS<1:0> = 10 and RL_SSR = 1                                 |                                        |                                        | BS RAM = 256 0x3F00                    | BS RAM = 1024 0x3C00                         |

|                                                                    | 0x3FFF                                 | BS RAM = 128                           | 0x3FFF                                 | 0x3FFF                                       |

| RSS<1:0> = 10 and RL_SSR = 0                                       | GS RAM = 14080 0x0800                  | GS RAM = 14080 0x0800                  | GS RAM = 14080 0x0800                  | GS RAM = 13312 0x0800                        |

| or<br>RSS<1:0> = 01 AND RL_SSR = 1                                 | SS RAM = 256 0x3F00                    | SS RAM = 128                           | BS RAM = 256 0x3F00                    | BS RAM = 1024 0x3C00                         |

|                                                                    | UX3FFF                                 | UX3FFF                                 | UX3FFF                                 | UX3FFF                                       |

|                                                                    | GS RAM = 12288 0x0800                        |

| RSS<1:0> = 01 AND RL_SSR = 0<br>OR<br>RSS<1:0> = 00 AND RL_SSR = 1 | SS RAM = 2048 0x3800                   | SS RAM = 1920 0x3800                   | SS RAM = 1792 0x3800                   | SS RAM = 1024 0x3800<br>BS RAM = 1024 0x3C00 |

|                                                                    | 0x3FFF                                 | BS RAM = 128 0x3F80 0x3FFF             | BS RAM = 256  0x3F00  0x3FFF           | 0x3FFF                                       |

|                                                                    | GS RAM = 10240<br>SS RAM = 4096 0x3000 | GS RAM = 10240<br>SS RAM = 3968 0x3000 | GS RAM = 10240<br>SS RAM = 3840 0x3000 | GS RAM = 10240 0x0800                        |

| RSS<1:0> = 00 AND RL_SSR = 0                                       |                                        | 33 TANVI = 3300                        | 00 IANIVI = 3040                       | SS RAM = 3072 0x3000                         |

|                                                                    |                                        | BS RAM = 128 0x3F80                    | BS RAM = 256 0x3F00                    | BS RAM = 1024 0x3C00                         |

|                                                                    | 0x3FFF                                 | 0x3FFF                                 | 0x3FFF                                 | 0x3FFF                                       |

dsPIC33F Family Reference Manual

Legend: OR = Logical OR, AND = Logical AND

DS70199B-page 23-11

Table 23-5: Data RAM Segment Sizes for Devices with 8 KB RAM

| CONFIGURATION BITS                                                 | RBS<1:0> = 11<br>OR<br>RBS<1:0> = 10 AND RL_BSR = 1 | RBS<1:0> = 10 AND RL_BSR = 0<br>OR<br>RBS<1:0> = 01 AND RL_BSR = 1 | RBS<1:0> = 01 AND RL_BSR = 0<br>OR<br>RBS<1:0> = 00 AND RL_BSR = 1 | RBS<1:0> = 00 AND RL_BSR = 0                |

|--------------------------------------------------------------------|-----------------------------------------------------|--------------------------------------------------------------------|--------------------------------------------------------------------|---------------------------------------------|

| RSS<1:0> = 11                                                      | GS RAM = 6144 0x0800                                | GS RAM = 6016 0x0800                                               | GS RAM = 5888 0x0800                                               | GS RAM = 5120 0x0800                        |

| OR<br>RSS<1:0> = 10 AND RL_SSR = 1                                 |                                                     |                                                                    | BS RAM = 256 0x1F00                                                | BS RAM = 1024 0x1C00                        |

|                                                                    | 0x1FFF                                              | BS RAM = 128                                                       | 0x1FFF                                                             | 0x1FFF                                      |

| RSS<1:0> = 10 AND RL_SSR = 0                                       | GS RAM = 5888 0x0800                                | GS RAM = 5888 0x0800                                               | GS RAM = 5888 0x0800                                               | GS RAM = 5120 0x0800                        |

| OR<br>RSS<1:0> = 01 AND RL_SSR = 1                                 | SS RAM = 256 0x1F00                                 | SS RAM = 128 0x1F00                                                | BS RAM = 256 0x1F00                                                | BS RAM = 1024 0x1C00                        |

|                                                                    | 0x1FFF                                              | BS RAM = 128  0x1F80  0x1FFF                                       | 0x1FFF                                                             | 0x1FFF                                      |

|                                                                    | GS RAM = 4096 0x0800                                | GS RAM = 4096 0x0800                                               | GS RAM = 4096 0x0800                                               | GS RAM = 4096 0x0800                        |

| RSS<1:0> = 01 AND RL_SSR = 0<br>OR<br>RSS<1:0> = 00 AND RL_SSR = 1 | SS RAM = 2048 0x1800                                | SS RAM = 1920 0x1800                                               | SS RAM = 1792  0x1800  0x1F00                                      | SS RAM = 1024  BS RAM = 1024  0x1800 0x1C00 |

|                                                                    | 0x1FFF                                              | BS RAM = 128                                                       | BS RAM = 256 0x1FFF 0x1FFF                                         | 0x1FFF                                      |

|                                                                    | GS RAM = 2048<br>SS RAM = 4096 0x1000               | GS RAM = 2048  0x0800  0x1000                                      | GS RAM = 2048<br>SS RAM = 3840 0x1000                              | GS RAM = 2048 0x0800 0x1000                 |

| RSS<1:0> = 00 AND RL_SSR = 0                                       |                                                     |                                                                    | 0x1F00                                                             | SS RAM = 3072 0x1C00                        |

|                                                                    | 0x1FFF                                              | BS RAM = 128                                                       | BS RAM = 256 0x1FFF 0x1FFF                                         | BS RAM = 1024<br>0x1FFF                     |

**Legend:** OR = Logical OR, AND = Logical AND

Note: If the defined Boot Segment size is greater than, or equal to, the defined Secure Segment, then the Secure Segment size selection has no effect and the Secure Segment is disabled.

Section 23. CodeGuard™ Security

DS70199B-page 23-12

Table 23-6: Program Flash Segment Sizes for 256 KB Devices

| CONFIGURATION BITS   | BSS<2:0> = x11 0K                  | BSS<2:0> = x10 1K                                        | BSS<2:0> = x01 4K                             | BSS<2:0> = x00 8K                                         |

|----------------------|------------------------------------|----------------------------------------------------------|-----------------------------------------------|-----------------------------------------------------------|

|                      | VS = 256 IW 0x000000<br>0x000200   | VS = 256 IW 0x000000<br>0x000200<br>0x000800             | VS = 256 IW 0x000000<br>BS = 3840 IW 0x000200 | VS = 256 IW 0x000000<br>BS = 7936 IW 0x000200             |

| SSS<2:0> = x11<br>0K |                                    |                                                          | 0x002000                                      | 0x004000                                                  |

|                      | GS = 87296 IW 0x02ABFE             | GS = 86528 IW 0x02ABFE                                   | GS = 83456 IW 0x02ABFE                        | GS = 79360 IW 0x02ABFE                                    |

| 222                  | VS = 256 IW 0x000000<br>0x000200   | VS = 256 IW                                              | VS = 256 IW 0x000000<br>BS = 3840 IW 0x000200 | VS = 256 IW 0x000000<br>BS = 7936 IW 0x000200             |

| SSS<2:0> = x10<br>8K | SS = 7936 IW 0x004000              | SS = 7168 IW 0x004000                                    | SS = 4096 IW 0x002000<br>0x004000             | 0x004000                                                  |

|                      | GS = 79360 IW 0x02ABFE             | GS = 79360 IW 0x02ABFE                                   | GS = 79360 IW 0x02ABFE                        | GS = 79360 IW 0x02ABFE                                    |

|                      | VS = 256 IW 0x000000<br>0x000200   | VS = 256 IW 0x000000<br>BS = 768 IW 0x000200             | VS = 256 IW 0x000000<br>BS = 3840 IW 0x000200 | VS = 256 IW 0x000000<br>BS = 7936 IW 0x000200             |

| SSS<2:0> = x01       |                                    | 0x000800                                                 | 0x002000                                      | SS = 8192 IW 0x004000                                     |

| 16K                  | SS = 16128 IW 0x008000             | SS = 15360 IW 0x008000                                   | SS = 12288 IW 0x008000                        | 0x008000                                                  |

|                      | GS = 71168 IW 0x02ABFE             | GS = 71168 IW 0x02ABFE                                   | GS = 71168 IW 0x02ABFE                        | GS = 71168 IW 0x02ABFE                                    |

|                      | VS = 256 IW 0x000000<br>0x000200   | VS = 256 IW 0x000000<br>BS = 768 IW 0x000200<br>0x000800 | VS = 256 IW 0x000000<br>BS = 3840 IW 0x000200 | VS = 256 IW 0x000000<br>BS = 7936 IW 0x000200<br>0x004000 |

| SSS<2:0> = x00       | SS = 32512 IW                      | SS = 31744 IW                                            | 0x002000<br>SS = 28672 IW                     | SS = 24576 IW                                             |

| 5-11                 | GS = 54784 IW 0x010000<br>0x02ABFE | GS = 54784 IW 0x010000<br>0x02ABFE                       | GS = 54784 IW 0x010000 0x02ABFE               | 0x010000<br>GS = 54784 IW<br>0x02ABFE                     |

**Legend:** IW = Instruction Words

DS70199B-page 23-13

Table 23-7: Program Flash Segment Sizes for 128 KB Devices

| CONFIGURATION BITS      | BSS<2:0> = x11 0K                | BSS<2:0> = x10 1K                                        | BSS<2:0> = x01 4K                             | BSS<2:0> = x00 8K                             |

|-------------------------|----------------------------------|----------------------------------------------------------|-----------------------------------------------|-----------------------------------------------|

| SSS<2:0> = x11<br>0K    | VS = 256 IW 0x000000<br>0x000200 | VS = 256 IW 0x000000<br>0x000200<br>0x000800             | VS = 256 IW 0x000000<br>0x000200<br>0x002000  | VS = 256 IW 0x000000<br>0x000200<br>0x004000  |

|                         | GS = 43776 IW 0x0157FE 0x02ABFE  | GS = 43008 IW 0x0157FE 0x02ABFE                          | GS = 39936 IW 0x0157FE 0x02ABFE               | GS = 35840 IW 0x0157FE 0x02ABFE               |

|                         | VS = 256 IW 0x000000<br>0x000200 | VS = 256 IW 0x000000<br>BS = 768 IW 0x000200<br>0x000800 | VS = 256 IW 0x000000<br>BS = 3840 IW 0x000200 | VS = 256 IW 0x000000<br>BS = 7936 IW 0x000200 |

| SSS<2:0> = x10<br>8K    | SS = 7936 IW 0x004000            | SS = 7168 IW 0x004000                                    | SS = 4096 IW 0x002000<br>0x004000             | 0x004000                                      |

|                         | GS = 35840 IW 0x0157FE 0x02ABFE  | GS = 35840 IW 0x0157FE 0x02ABFE                          | GS = 35840 IW 0x0157FE 0x02ABFE               | GS = 35840 IW 0x0157FE 0x02ABFE               |

|                         | VS = 256 IW 0x000000<br>0x000200 | VS = 256 IW 0x000000<br>BS = 768 IW 0x000200<br>0x000800 | VS = 256 IW 0x000000<br>BS = 3840 IW 0x000200 | VS = 256 IW 0x000000<br>BS = 7936 IW 0x000200 |

| SSS<2:0> = x01<br>16K   | SS = 16128 IW                    | SS = 15360 IW                                            | 0x002000<br>SS = 12288 IW<br>0x008000         | 0x004000<br>SS = 8192 IW<br>0x008000          |

|                         | GS = 27648 IW 0x0157FE 0x02ABFE  | GS = 27648 IW 0x0157FE 0x02ABFE                          | GS = 27648 IW 0x0157FE 0x02ABFE               | GS = 27648 IW 0x0157FE 0x02ABFE               |

|                         | VS = 256 IW 0x000000<br>0x000200 | VS = 256 IW 0x000000<br>BS = 768 IW 0x000200<br>0x000800 | VS = 256 IW 0x000000<br>BS = 3840 IW 0x000200 | VS = 256 IW 0x000000<br>BS = 7936 IW 0x000200 |

| SSS<2:0> = x00<br>32K   | SS = 32512 IW                    | SS = 31744 IW                                            | 0x002000<br>SS = 28672 IW                     | 0x004000<br>SS = 24576 IW                     |

| Legend: IW = Instructio | GS = 11264 IW                    | GS = 11264 IW                                            | GS = 11264 IW                                 | GS = 11264 IW                                 |

**Legend:** IW = Instruction Words

DS70199B-page 23-14

Table 23-8: Program Flash Segment Sizes for 64 KB Devices

| CONFIGURATION BITS        | BSS<2:0> = x11 0K                          | BSS<2:0> = x10 1K                                     | BSS<2:0> = x01 4K                                        | BSS<2:0> = x00 8K                                       |

|---------------------------|--------------------------------------------|-------------------------------------------------------|----------------------------------------------------------|---------------------------------------------------------|

| SSS<2:0> = x11            | VS = 256 IW 0x000000                       | VS = 256 IW                                           | VS = 256 IW 0x000000 0x000200 0x002000                   | VS = 256 IW                                             |

| 0K                        | GS = 21760 IW 0x00ABFE 0x02ABFE            | GS = 20992 IW 0x00ABFE 0x02ABFE                       | GS = 17920 IW 0x00ABFE 0x02ABFE                          | GS = 13824 IW 0x00ABFE 0x02ABFE                         |

| SSS<2:0> = x10            | VS = 256 IW                                | VS = 256 IW                                           | VS = 256 IW 0x000000 0x000200 0x000200                   | VS = 256 IW                                             |

| 4K                        | GS = 17920 IW 0x00ABFE 0x02ABFE            | GS = 17920 IW 0x00ABFE 0x02ABFE                       | GS = 17920 IW 0x00ABFE 0x02ABFE                          | GS = 13824 IW 0x00ABFE 0x02ABFE                         |

| \$\$\$<2:0> = x01         | VS = 256 IW 0x000000<br>0x000200           | VS = 256 IW 0x000000<br>0x000200<br>0x000800          | VS = 256 IW 0x000000<br>BS = 3840 IW 0x000200            | VS = 256 IW 0x000000<br>BS = 7936 IW 0x000200           |

| 8K                        | SS = 7936 IW 0x004000 0x00ABFE             | SS = 7168 IW 0x004000<br>GS = 13824 IW 0x00ABFE       | SS = 4096 IW                                             | 0x004000<br>GS = 13824 IW<br>0x00ABFE                   |

|                           | 0x02ABFE  VS = 256 IW  0x000000  0x0000200 | 0x02ABFE  VS = 256 IW  BS = 768 IW  0x000200 0x000800 | 0x02ABFE<br>VS = 256 IW<br>BS = 3840 IW<br>0x000200      | 0x02ABFE  VS = 256 IW  BS = 7936 IW  0x000200           |

| SSS<2:0> = x00<br>16K     | SS = 16128 IW                              | SS = 15360 IW  GS = 5632 IW  0x008000 0x00ABFE        | SS = 12288 IW  GS = 5632 IW  0x002000  0x008000 0x00ABFE | Ox004000  SS = 8192 IW  GS = 5632 IW  Ox008000 Ox00ABFE |

| La recorde DM Instruction | 0x02ABFE                                   | 0x02ABFE                                              | 0x02ABFE                                                 | 0x02ABFE                                                |

**Legend:** IW = Instruction Words

Table 23-9: Program Flash Segment Sizes for 32KB Devices

| BSS<2:0> = x11 0K              | BSS<2:0> = x10 1K              |

|--------------------------------|--------------------------------|

| VS = 256 IW                    | VS = 256 IW                    |

| 0x0057FE                       | 0x0057FE                       |

| BSS<2:0> = x01 4K              | BSS<2:0> = x00 8K              |

| BSS<2:0> = x01 4K  VS = 256 IW | BSS<2:0> = x00 8K  VS = 256 IW |

Legend: IW = Instruction Words

Table 23-10: Program Flash Segment Sizes for 16 KB Devices

| BSS<2:0> = x11 0K                            | BSS<2:0> = x10 1K                                                                |

|----------------------------------------------|----------------------------------------------------------------------------------|

| VS = 256 IW 0x000000<br>0x0001FE<br>0x000200 | VS = 256 IW 0x000000<br>0x0001FE<br>0x000200<br>0x0007FE<br>0x00078E<br>0x000800 |

| GS = 5376 IW 0x002BFE 0x002C00               | GS = 4608 IW 0x002BFE 0x002C00                                                   |

| 0x0057FE                                     | 0x0057FE                                                                         |

| 200 00 416                                   | 000 000 000                                                                      |

| BSS<2:0> = x01 4K                            | BSS<2:0> = x00 8K                                                                |

| BSS<2:0> = x01 4K  VS = 256 IW               | BSS<2:0> = x00 8K    VS = 256 IW                                                 |

| VS = 256 IW 0x000000<br>0x0001FE             | VS = 256 IW 0x000000<br>0x0001FE<br>0x0001FE                                     |

**Legend:** IW = Instruction Words

Table 23-11: Program Flash Segment Sizes for 12 KB Devices

| Table 23-11. Flogram Flash Segment Sizes | 10. 12.12.2011000                                                    |

|------------------------------------------|----------------------------------------------------------------------|

| CONFIG BITS                              |                                                                      |

|                                          | VS = 256 IW 0x000000<br>0x0001FE<br>0x000200                         |

| BSS<2:0> = x11 0K                        | GS = 3840 IW 0x001FFE                                                |

| BSS<2:0> = x10 256                       | VS = 256 IW 0x000000<br>0x0001FE<br>0x000200<br>0x0003FE<br>0x000400 |

|                                          | GS = 3584 IW 0x001FFE                                                |

|                                          | VS = 256 IW 0x000000<br>0x0001FE<br>0x000200                         |

| BSS<2:0> = x01 768                       | BS = 768 IW<br>0x0007FE<br>0x000800                                  |

|                                          | GS = 3072 IW 0x001FFE                                                |

|                                          | VS = 256 IW 0x000000<br>0x0001FE<br>0x000200                         |

| BSS<2:0> = x00 1792                      | BS = 1792 IW                                                         |

|                                          | 0x000FFE<br>0x001000<br>0x001FFE                                     |

**Legend:** IW = Instruction Words

lote: The

The segment organizations shown in Table 23-3 through Table 23-11 are typical, but some devices may differ. To verify the memory segment sizes for different settings, refer to the specific device data sheets.

## 23.6.2 Selecting the Security Level of the Boot Segment

The security level of the Boot Segment is determined by the Configuration bit BSS2 (FBS<3>):

- 1 = Standard security

- 0 = High security

When the Boot Segment is configured for high security, the number of access methods is more limited than with standard security. The differences are noted in the following paragraphs. For additional information, refer to **Section 23.11 "Rules Concerning Program Flow"**.

## 23.6.3 Write Protection of the Boot Segment

The Boot Segment can be write-protected by programming Configuration bit BWRP (FBS<0>):

- 1 = Boot segment can be written

- 0 = Boot segment is write-protected

When write-protected, page erase and programming operations targeting the Boot Segment of program Flash are disabled. Setting the WR bit within the NVMCON Special Function Register will not start an operation. Erase operations that erase the entire Boot Segment are allowed; however, the Secure and General Segments are also erased.

## 23.6.4 Allocating Boot Segment RAM

The Boot Segment can also allocate a portion of the data RAM memory of the device for exclusive access by code executing within the Boot Segment. This protects the data integrity of algorithms executing within the Boot Segment.

If a Boot Segment is not allocated, BSS<2:0> = x11 (FBS<3:1>), then a RAM segment cannot be allocated. The existence and size of Boot Segment RAM are determined by the RBS<1:0> (FBS<7:6>) Configuration bits.

One of the options is to exclude the Boot Segment RAM, which is the default option on an erased, non-programmed device.

Figure 23-4 shows that the Boot Segment RAM is located at the end of data RAM, or at the last location before the DMA memory area. The Boot Segment RAM starts at an address specified by the RBS<1:0> bits.

**Note:** DMA RAM is not present on all dsPIC33F devices. For DMA RAM availability and sizes, refer to the specific device data sheet.

Figure 23-4: Secure Segment Data RAM Allocation

Table 23-12 shows an example of Boot Segment RAM size options for dsPIC33F devices. The start addresses listed are typical. For specific addresses, refer to the device data sheet.

Table 23-12: Boot Segment RAM Size Example

| RBS<1:0> | BS<br>Size / Bytes | BS Start<br>Address | BS End<br>Address |  |  |  |

|----------|--------------------|---------------------|-------------------|--|--|--|

| 11       |                    | No Boot Segment     |                   |  |  |  |

| 10       | Small/128          | EOM-0x007F          | EOM               |  |  |  |

| 01       | Medium/256         | EOM-0x00FF          | EOM               |  |  |  |

| 0.0      | Large/1024         | EOM-0x03FF          | EOM               |  |  |  |

**Note:** EOM refers to the last location of data RAM excluding DMA RAM.

## 23.6.5 Run Time Release of Boot Segment RAM

When an algorithm within the Boot Segment completes its task and is preparing to return execution to code within a lower priority segment, it can be helpful to release some of the RAM allocated to the Boot Segment. The Boot Segment RAM control Special Function Register (SFR) contains the RL\_BSR (BSRAM<0>) bit (refer to Register 23-2). When this bit is set, the system releases a portion of the BS RAM back to the next lower priority segment defined. Table 23-13 is an example of RAM mapped with RL\_BSR = '0' and RL\_BSR = '1'.

Table 23-13: Boot Segment RAM Release

| DDC 44.0 | BS Size when:   |                 |  |  |

|----------|-----------------|-----------------|--|--|

| RBS<1:0> | RL_BSR = 0      | RL_BSR = 1      |  |  |

| 11       | No Boot Segment |                 |  |  |

| 10       | Small           | No Boot Segment |  |  |

| 01       | Medium Small    |                 |  |  |

| 00       | Large           | Medium          |  |  |

## 23.6.6 Releasing the Secure RAM for General Use

The secure code segments can release some allocation of its secure RAM for general use at any time during operation. For example, the minimum allocation can be reserved for the BS to store sensitive volatile variables during General Segment code run time. Then, when the code branches to the BS segment to execute an algorithm, the BS code can clear the RL\_BSR bit to secure the maximum allocation of the secure RAM for its use. After the BS code execution completes, it can set the RL\_BSR bit to again minimize the allocated secure RAM.

Both the Boot and Secure Segments have an associated BSRAM and SSRAM register, which contains the RL\_BSR or RL\_SSR bits respectively. Only BS segment has write access to the BSRAM register, and only Secure Segment has write access to the SSRAM register.

**Note:** On any reset, the maximum allocations are in a secure state because the RL\_BSR and RL\_SSR bits are Reset.

The RAM security bits determine whether RAM is secured or not.

- If RSS<1:0> = 11 (FSS<7:6>), no secure RAM is allocated and the RL\_SSR bit is ignored

- If RBS<1:0> = 11 (FBS<7:6>), no boot RAM is allocated and the RL\_BSR bit is ignored

## 23

# codeGuard™ Security

#### Register 23-2: BSRAM: Boot Segment RAM Special Function Register

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | -   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | R-0    | R-0    | R/W-0  |

|-------|-----|-----|-----|-----|--------|--------|--------|

| _     | _   | _   | _   | _   | IW_BSR | IR_BSR | RL_BSR |

| bit 7 |     |     |     |     |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 **Unimplemented:** Read as '0' bit 2 **IW\_BSR** (Read-Only Status bit)

0 = No illegal write has been attempted since this register was last read

1 = At least one illegal write has been attempted since last read of this register

IW\_BSR bit is cleared on any Reset. It is also cleared AFTER the BSRAM register is read while

executing in BS.

bit 1 IR\_BSR (Read-Only Status bit)

0 = No invalid read of protected BS RAM section has occurred since this register was last read

1 = At least one invalid read has occurred since last read of this register

IR\_BSR bit is cleared on any Reset. It is also cleared AFTER the BSRAM register is read while

executing in BS.

bit 0 RL\_BSR

0 = BSRAM is held secure for BS only

$_{

m 1}\,$  = BS has released the secure RAM for general use. All but the highest 128 bytes are released

RL\_BSR bit is cleared to zero on any Reset.

## 23.7 THE SECURE SEGMENT

The Secure Segment has the second highest privilege and is ideal for storing proprietary algorithm routines. Access to the Secure Segment from lower priority segments are limited to "calls" to the Secure Segment.

## 23.7.1 Allocating the Secure Segment

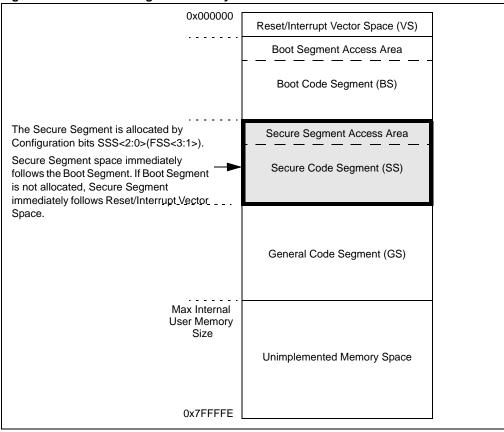

The Secure Segment is allocated by the Configuration bits SSS<2:0> (FSS<3:1>).

Figure 23-5 shows the Secure Segment begins immediately following the Boot Segment. If there is no Boot Segment, the Secure Segment starts at the end of the Reset/Interrupt Vector Space. The default is to exclude a Secure Segment.

Figure 23-5: Secure Segment Memory Allocation

The Secure Segment continues to an address specified by the SSS<2:0> bits. Table 23-14 shows an example of Secure Segment options (in this case, for devices with 64 KB flash memory). The end addresses listed in these tables are typical. Refer to the device data sheet for specific addresses for a given device.

Table 23-14: Secure Segment Size Example

| SSS<2:0> | Security Level | SS<br>Size       | SS Start<br>Address | SS End<br>Address |

|----------|----------------|------------------|---------------------|-------------------|

| x11      |                | No Secure Progra | m Flash Segment     |                   |

| 110      | Standard       | Small            | E.O. BS + 1         | 0x001FFE          |

| 010      | High           | Small            | E.O. BS + 1         | 0x001FFE          |

| 101      | Standard       | Medium           | E.O. BS + 1         | 0x003FFE          |

| 001      | High           | Medium           | E.O. BS + 1         | 0x003FFE          |

| 100      | Standard       | Large            | E.O. BS + 1         | 0x007FFE          |

| 000      | High           | Large            | E.O. BS + 1         | 0x007FFE          |

Note: E.O. BS refers to the last location of the Boot Segment.

#### Register 23-3: FSS: Secure Segment Configuration Register Byte

| R/P   | R/P  | U | U | R/P  | R/P  | R/P  | R/P   |

|-------|------|---|---|------|------|------|-------|

| RSS1  | RSS0 | R | R | SSS2 | SSS1 | SSS0 | SWRP  |

| bit 7 |      |   |   |      |      |      | bit 0 |

| Legend:           |                  |                       |                    |

|-------------------|------------------|-----------------------|--------------------|

| R = Readable bit  | W = Writable bit | U = Unimplemented bit | , read as '0'      |

| -n = Value at POR | '1' = Bit is set | '0' = Bit is cleared  | x = Bit is unknown |

bit 7-6 RSS<1:0>: Secure Segment RAM Code Protection bits<sup>(1)</sup>

11 = No Secure RAM defined

10 = Secure RAM is 256 Bytes less BS RAM 01 = Secure RAM is 2048 Bytes less BS RAM 00 = Secure RAM is 4096 Bytes less BS RAM

bit 5-4 Reserved: Programming values will have no effect

bit 3-1 SSS<2:0>: Secure Segment Program Flash Code Protection bits<sup>(2)</sup>

x11 = No Secure program Flash segment

110 = Standard security, Small Secure Segment

010 = High security, Small Secure Segment

101 = Standard security, Medium Secure Segment

001 = High security, Medium Secure Segment

100 = Standard security, Large Secure Segment

000 = High security, Large Secure Segment

For device specific information see Table 23-8.

bit 0 SWRP: Secure Segment Program Flash Write Protection

1 = Secure Segment can be written0 = Secure Segment is write-protected

**Note 1:** Not all devices have Secure Segment RAM code protection. For device specific information refer to Table 23-3, Table 23-4 and Table 23-5.

- 2: The exact definitions of Small, Medium, and Large Secure Segment vary from one device to another. For device specific information refer to Table 23-6, Table 23-7 and Table 23-8.

- 3: If a Secure Segment is not needed, the SWRP bit must be programmed as a "1".

### 23.7.2 Selecting the Security Level of the Secure Segment

The security level of the secure code segment is determined by the Configuration bit SSS2 (FSS<3>):

- 1 = Standard security

- 0 = High security

When the Secure Segment is configured for high security, the number of access methods is more limited than with standard security. The differences are noted in the following paragraphs.

## 23.7.3 Write Protection of the Secure Segment

The Secure Segment can be write-protected by programming the SWRP (FSS<0>) Configuration bit.

- 1 = Secure Segment can be written

- 0 = Secure Segment is write-protected

When write-protected, or page erase and programming operations targeting the Secure Segment of program Flash are disabled, setting the WR bit within the NVMCON Special Function Register will not start an operation. Erase operations that erase the entire Secure Segment are allowed; however, the General Segment is also erased.

## 23.7.4 Allocating Secure Segment RAM

The Secure Segment can also allocate a portion of the data RAM for code protection. However, if a Secure Segment is not allocated, SSS<2:0> =  $\times 11$  (FSS<3:1>), then a RAM segment cannot be allocated. The existence and size of Secure Segment RAM are determined by the RSS<1:0> (FSS<7:6>) Configuration bits.

One of the options is to exclude the Secure Segment RAM, which is the default option on an erased, non-programmed device.

The Secure Segment RAM ends at the last location before the Boot Segment RAM. The Secure Segment RAM starts at an address specified by the RSS<1:0> bits.

Secure Segment data RAM is allocated to code protection by the RSS Configuration bits in the FSS register.

End of Non-DMA RAM

Boot Segment Data RAM

Boot Segment Data RAM

DMA RAM

Unused Space

PSV Window

0xFFFE

Figure 23-6: Secure Segment Data RAM Allocation

Table 23-15 shows an example of Secure Segment RAM allocations. The start addresses listed are typical. Refer to the device data sheet for specific addresses for a given device.

Table 23-15: Secure Segment RAM Size Example

| RSS<1:0> | SS<br>Size | SS Start<br>Address   | SS End<br>Address |  |  |  |

|----------|------------|-----------------------|-------------------|--|--|--|

| 11       |            | No Secure Segment     |                   |  |  |  |

| 10       | Small      | Small S.O.BS-0x0100 S |                   |  |  |  |

| 01       | Medium     | S.O.BS-0x0800         | S.O.BS-1          |  |  |  |

| 00       | Large      | S.O.BS-0x1000         | S.O.BS-1          |  |  |  |

Note: S.O. BS refers to the first location of basic segment data RAM.

## 23.7.5 Run Time Release of Secure Segment RAM

Like the Boot Segment, the Secure Segment can allocate and release RAM. The Secure Segment RAM control Special Function Register (SFR) contains the RL\_SSR (SSRAM<0>) bit (refer to Register 23-4). When this bit is set, the system releases a portion of the Secure Segment RAM back to the next lower priority segment defined. Table 23-16 is an example of RAM mapped with RL\_SSR = '0' and RL\_SSR = '1'.

Table 23-16: Secure Segment RAM Release

| DSC -41-0- | Secure Segment Size When: |                   |  |  |

|------------|---------------------------|-------------------|--|--|

| RSS<1:0>   | RL_SSR = 0                | RL_SSR = 1        |  |  |

| 11         | No Secure Segment         |                   |  |  |

| 10         | Small                     | No Secure Segment |  |  |

| 01         | Medium                    | Small             |  |  |

| 0.0        | Large Medium              |                   |  |  |

## 23.7.6 Releasing Secure Segment RAM for General Use

The secure code segments can release some allocation of its secure RAM for general use at any time during operation. For example, the minimum allocation can be reserved for the Secure Segment to store sensitive volatile variables during General Segment code run time. When the code branches to the Secure Segment to execute an algorithm, the Secure Segment code can clear the RL\_SSR bit to secure the maximum allocation of the secure RAM for its use. After the Secure Segment code execution completes, it can set the RL\_SSR bit to again minimize the allocated secure RAM.

Both the Boot and Secure Segments have an associated BSRAM and SSRAM register, which contains the RL\_BSR or RL\_SSR bits, respectively. Only the Boot Segment has write access to the BSRAM register, and only the Secure Segment has write access to the SSRAM register.

Note that on any Reset, because the RL\_SSR bit is Reset, the maximum allocations are in a secure state.

The RAM security bits determine whether RAM is secured or not. If RSS<1:0> = 11 (FSS<7:6>), no secure RAM is allocated and the RL\_SSR bit is "don't care."

## dsPIC33F Family Reference Manual

#### Register 23-4: SSRAM: Secure Segment RAM Special Function Register

| U-0    | U-0 | U-0 | U-0 | U-0 | U-0 | U-0 | U-0   |

|--------|-----|-----|-----|-----|-----|-----|-------|

| _      | _   | _   | _   | _   | _   | _   | _     |

| bit 15 |     |     |     |     |     |     | bit 8 |

| U-0   | U-0 | U-0 | U-0 | U-0 | U-0    | R-0    | R-0    |

|-------|-----|-----|-----|-----|--------|--------|--------|

| _     | _   | _   | _   | _   | IW_SSR | IR_SSR | RL_SSR |

| bit 7 |     |     |     |     |        |        | bit 0  |

Legend:

R = Readable bit W = Writable bit U = Unimplemented bit, read as '0'

-n = Value at POR '1' = Bit is set '0' = Bit is cleared x = Bit is unknown

bit 15-3 **Unimplemented:** Read as '0' bit 2 **IW\_SSR** (Read-Only Status bi

IW\_SSR (Read-Only Status bit)

0 = No illegal write of protected SSRAM has been attempted since this register was last read

1 = At least one illegal write has been attempted since last read of this register

IW\_SSR bit is cleared on any Reset. It is also cleared AFTER SSRAM register is read while executing

in Secure Segment.

bit 1 IR\_SSR (Read-Only Status bit)

0 = No invalid read of protected SSRAM has occurred since this register was last read

1 = At least one invalid read has occurred since last read of this register

IR\_SSR bit cleared on any Reset. It is also cleared AFTER SSRAM register is read while executing in

Secure Segment.

bit 0 RL\_SSF

0 = SSRAM is held secure for Secure Segment only

1 = Secure Segment has released the secure RAM for general use. All but the highest 128 bytes are released

RL\_SSR bit is cleared to zero on any Reset.

## 23.8 THE GENERAL SEGMENT

The General Segment has the lowest security privilege level. The General Segment is intended to contain the majority of the application code. Its size is essentially the on-chip memory minus the Boot and Secure Segments. If there are no Boot or Secure Segments, the General Segment uses all of the on-chip memory.

## 23.8.1 Allocating the General Segment

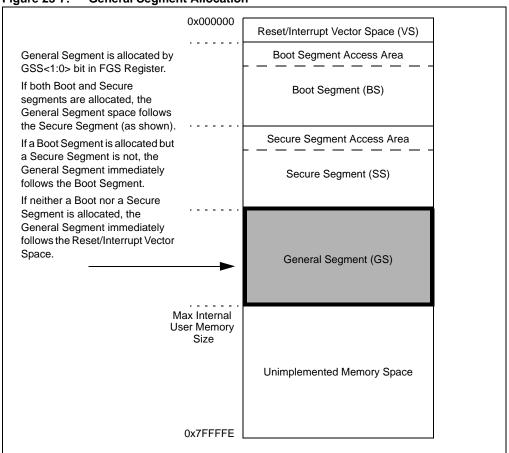

The General Segment always exists, regardless of whether Boot and Secure Segments are allocated. It is specified by the GSS<1:0> Configuration bit in the FGS register. The location of the General Segment depends on the existence of the Boot and Secure Segments.

Figure 23-7 shows that if both Boot and Secure Segments are allocated, the General Segment immediately follows the Secure Segment. If a Boot Segment is allocated, but a Secure Segment is not, the General Segment immediately follows the Boot Segment. If neither a Boot Segment nor a Secure Segment is allocated, the General Segment immediately follows the Reset/Interrupt Vector Space (VS).

The device default is to exclude Boot and Secure Segments. By default, the entire program memory is allocated as General Segment.

Figure 23-7: General Segment Allocation

# dsPIC33F Family Reference Manual

## Register 23-5: FGS: General Segment Configuration Register

| U     | U | U | U | U | R/P  | R/P  | R/P   |

|-------|---|---|---|---|------|------|-------|

| R     | R | R | R | R | GSS1 | GSS0 | GWRP  |

| bit 7 |   |   |   |   |      |      | bit 0 |

Legend:R = Readable bitW = Writable bitU = Unimplemented bit, read as '0'-n = Value at POR'1' = Bit is set'0' = Bit is clearedx = Bit is unknown

bit 7-3 Reserved: Used for silicon validation purposes

bit 2-1 GSS<1:0>: General Segment Program Flash Code Protection bits<sup>(1)</sup>

11 = General Segment not protected

10 = Standard security; general program Flash segment starts at end of SS and ends at EOM

0X = High security; general program Flash segment starts at end of SS and ends at EOM

bit 0 GWRP: General Segment Program Flash Write Protection

1 = General segment can be written

0 = General segment is write-protected

Note 1: On certain devices, GSS<1> is Reserved, and GSS<0> is referred to as the GCP bit.

## 23.8.2 Selecting the Security Level of the General Segment

Depending on the device, there are up to three levels of security to choose for the General Segment. Refer to the specific device data sheet to determine how many options are available.

Configuration bits GSS<1:0> (FGS<2:1>) determine the level of protection for this segment:

- 11 = No protection

- 10 = Standard security

- 0X = High security

## 23.8.3 Write Protection of the General Segment

The General Segment can be write-protected by programming the GWRP (FGS<0>) Configuration bit, similarly to write protecting the Boot Segment:

- 1 = General code segment can be written

- 0 = General code segment is write-protected

## 23.9 THE RESET, TRAP AND INTERRUPT SERVICE ROUTINE VECTOR SPACE

The first 256 instruction words are reserved for the RESET instruction, trap, and interrupt vectors.

Protection of this segment depends on the state of the BSS<2:0> (FBS<3:1>) and GSS<1:0> (FGS<2:1>) or GCP (FGS<1>) code protection bits. If a Boot Segment is allocated, the Vector Space protection is the same as the Boot Segment. In other words, if a Boot Segment is defined, erase and programming operations of the Vector Space can only be performed via Boot Segment code. If a Boot Segment is not allocated, the Vector Space protection is the same as the General Segment and erase and programming operations of the Vector Space can be performed via General Segment code.

A write to this segment is enabled or disabled by the BWRP bit if a Boot Segment is allocated, or by the GWRP bit if a Boot Segment is excluded.

## 23.10 DEFINITION OF SECURITY PRIVILEGES

It is important to understand the relative privilege levels of the three code protection segments. Operations can be described as being relative to higher or lower privilege segments. The Boot Segment has the highest privilege level and can directly access code in the lower segments. The Secure Segment can directly access code in the General Segment, but can only issue calls to code in the Boot Segment. The General Segment can only access code from either of the higher segments by issuing calls.

Rules governing access privileges are discussed in sections **23.11** "Rules Concerning Program Flow" through **23.14.1** "Rules for Programming Devices in RTSP". Table 23-17 presents a summary overview of these rules during normal run-time operation.

DS70199B-page 23-29

Table 23-17: Privileged Operations Rules Summary

| Target Segment                                               |                                                               |                                                                                          | General Segment |          |            |      |            | Secure Segment |            |            | Boot Segment |            |            |            | IVT and AIVT |                     |        |          |     |        |     |  |  |  |

|--------------------------------------------------------------|---------------------------------------------------------------|------------------------------------------------------------------------------------------|-----------------|----------|------------|------|------------|----------------|------------|------------|--------------|------------|------------|------------|--------------|---------------------|--------|----------|-----|--------|-----|--|--|--|

| Protection Level                                             |                                                               | None                                                                                     |                 | Standard |            | High |            | Standard       |            | High       |              | Standard   |            | High       |              | None                |        | Standard |     | High   |     |  |  |  |

| Write-Protected                                              |                                                               | No                                                                                       | Yes             | No       | Yes        | No   | Yes        | No             | Yes        | No         | Yes          | No         | Yes        | No         | Yes          | No                  | Yes    | No       | Yes | No     | Yes |  |  |  |

| Requested Operation (Yes/No                                  |                                                               |                                                                                          |                 |          |            |      |            |                |            |            |              |            |            |            |              |                     |        |          |     |        |     |  |  |  |

| PC Rollover into Target Segment                              |                                                               | Yes                                                                                      | Yes             | Yes      | Yes        | Yes  | Yes        | Yes            | Yes        | Yes        | Yes          | N/A        | N/A        | N/A        | N/A          | n/a <b>(Note 3)</b> |        |          |     |        |     |  |  |  |

| PFC from reset vector instruction to Target Segment (Note 5) |                                                               | Yes                                                                                      | Yes             | Yes      | Yes        | Yes  | Yes        | Yes            | Yes        | Note 2     | Note 2       | Yes        | Yes        | Note 2     | Note 2       | Note 4              |        |          |     |        |     |  |  |  |

| VFC (Vector Flow Change) to Target Segment (Note 5)          |                                                               | Yes                                                                                      | Yes             | Yes      | Yes        | Yes  | Yes        | Yes            | Yes        | Note 2     | Note 2       | Yes        | Yes        | Note 2     | Note 2       | Note 4              |        |          |     |        |     |  |  |  |

| PFC from BS to Target Segment (Note 1)                       |                                                               | Yes                                                                                      | Yes             | Yes      | Yes        | Yes  | Yes        | Yes            | Yes        | Yes        | Yes          | Yes        | Yes        | Yes        | Yes          |                     | Note 4 |          |     |        |     |  |  |  |

| PFC from SS to Target Segment (Note 1)                       |                                                               | Yes                                                                                      | Yes             | Yes      | Yes        | Yes  | Yes        | Yes            | Yes        | Yes        | Yes          | Yes        | Yes        | Note 2     | Note 2       |                     | Note 4 |          |     |        |     |  |  |  |

| PFC from GS to Target Segment (Note 1)                       |                                                               | Yes                                                                                      | Yes             | Yes      | Yes        | Yes  | Yes        | Yes            | Yes        | Note 2     | Note 2       | Yes        | Yes        | Note 2     | Note 2       |                     |        | Note     | e 4 |        |     |  |  |  |

| R/W of Target Segment RAM                                    | BS                                                            | Yes                                                                                      | Yes             | Yes      | Yes        | Yes  | Yes        | No             | No         | No         | No           | Yes        | Yes        | Yes        | Yes          |                     |        | n/a      | а   |        |     |  |  |  |

| while executing from:<br>Note: Stack assumed to be in GS     | SS                                                            | Yes                                                                                      | Yes             | Yes      | Yes        | Yes  | Yes        | Yes            | Yes        | Yes        | Yes          | No         | No         | No         | No           |                     |        |          |     |        |     |  |  |  |

| RAM space, access needed                                     | GS                                                            | Yes                                                                                      | Yes             | Yes      | Yes        | Yes  | Yes        | No             | No         | No         | No           | No         | No         | No         | No           |                     | -      |          | •   | 5.     |     |  |  |  |

| Table Read/PSV of Target<br>Segment Program Flash            | BS                                                            | Yes                                                                                      | Yes             | Yes      | Yes        | No   | No         | Yes            | Yes        | No         | No           | Yes        | Yes        | Yes        | Yes          | Yes                 | Yes    | Yes      | Yes | Yes    | Yes |  |  |  |

| while executing from:                                        | SS                                                            | Yes                                                                                      | Yes             | Yes      | Yes        | No   | No         | Yes            | Yes        | Yes        | Yes          | No         | No         | No         | No           | Yes                 | Yes    | Yes      | Yes | Yes    | Yes |  |  |  |

| (Note 7)                                                     | GS                                                            | Yes                                                                                      | Yes             | Yes      | Yes        | Yes  | Yes        | No             | No         | No         | No           | No         | No         | No         | No           | Yes                 | Yes    | Yes      | Yes | Yes    | Yes |  |  |  |

| Table Write of Target Segment (load write latches)           |                                                               | Yes                                                                                      | Yes             | Yes      | Yes        | Yes  | Yes        | Yes            | Yes        | Yes        | Yes          | Yes        | Yes        | Yes        | Yes          | Yes                 | Yes    | Yes      | Yes | Yes    | Yes |  |  |  |

| Program/Erase row                                            | BS                                                            | Yes                                                                                      | No              | Yes      | No         | No   | No         | Yes            | No         | No         | No           | Yes        | No         | Yes        | No           | Yes                 | No     | Yes      | No  | No     | No  |  |  |  |

| of Target Segment program Flash while executing from:        | SS                                                            | Yes                                                                                      | No              | Yes      | No         | No   | No         | Yes            | No         | Yes        | No           | No         | No         | No         | No           | Note 6              | No     | Note 6   | No  | Note 6 | No  |  |  |  |

|                                                              | GS                                                            | Yes                                                                                      | No              | Yes      | No         | Yes  | No         | No             | No         | No         | No           | No         | No         | No         | No           | Note 6              | No     | Note 6   | No  | Note 6 | No  |  |  |  |

| Erase Target Segment data flash while executing from:        | BS                                                            | Yes                                                                                      | Yes             | Yes      | Yes        | Yes  | Yes        | Yes            | Yes        | Yes        | Yes          | Yes        | Yes        | Yes        | Yes          |                     |        | n/a      | a   |        |     |  |  |  |

| Willo oxoodaling from:                                       | SS                                                            | Yes                                                                                      | Yes<br>Yes      | Yes      | Yes<br>Yes | Yes  | Yes<br>Yes | Yes<br>Yes     | Yes<br>Yes | Yes<br>Yes | Yes<br>Yes   | Yes<br>Yes | Yes<br>Yes | Yes<br>Yes | Yes<br>Yes   |                     |        |          |     |        |     |  |  |  |

| Erase All                                                    |                                                               | 163                                                                                      | 163             | 163      | 163        | 162  | 163        | 163            | 162        |            | nand not v   |            |            |            | 162          | 60                  |        |          |     |        |     |  |  |  |

| Erase BS Segment/code-protect                                | Erase GS/SS/BS/VS segments and GS/SS/BS code protection fuses |                                                                                          |                 |          |            |      |            |                |            |            |              |            |            |            |              |                     |        |          |     |        |     |  |  |  |

| Erase SS Segment/code-protect                                |                                                               | Erase GS/SS segments and GS/SS code protection fuses Erase VS if no Boot Segment defined |                 |          |            |      |            |                |            |            |              |            |            |            |              |                     |        |          |     |        |     |  |  |  |

| Erase GS Segment/code-protect                                |                                                               | Erase GS segment and GS code protection fuses Erase VS if no Boot Segment defined        |                 |          |            |      |            |                |            |            |              |            |            |            |              |                     |        |          |     |        |     |  |  |  |

| Erase GS Segment                                             |                                                               | Erase GS Segment Only                                                                    |                 |          |            |      |            |                |            |            |              |            |            |            |              |                     |        |          |     |        |     |  |  |  |

| Program configuration register                               |                                                               | Yes                                                                                      |                 |          |            |      |            |                |            |            |              |            |            |            |              |                     |        |          |     |        |     |  |  |  |

Note 1:PFC (Program Flow Change) is defined as when the PC is loaded with a new value instead of the normal automatic increment. It includes JUMP, CALL, RETURN, RETFIE, Computed Jump etc.

<sup>2:</sup>PFC is allowed only to the first 32 instruction locations of the segment.

<sup>3:</sup>Since execution is not permitted in the VS segment, this condition is not possible.

<sup>4:</sup>A PFC operation (i.e., branch, call etc.) into the IVT and AIVT segment is possible. But as soon as execution is attempted out of this segment an illegal address trap will result (unless pointed to Reset vector at address 0x000000).

<sup>5:</sup>VFC (Vector Flow Change) is defined as when the PC is loaded with a Interrupt or trap vector address.

**<sup>6:</sup>**Operation allowed if there is no higher security privilege-segment defined.

<sup>7:</sup>TBLRD or DS read will execute but return all 0s if not allowed.

## 23.11 RULES CONCERNING PROGRAM FLOW

Program flow refers to the execution sequence of program instructions in program memory. Normally, instructions are executed sequentially as the Program Counter (PC) increments. When code protection is implemented, program flow conforms to privilege level. That is, a program executing from code-protected memory can flow from a higher security segment to a lower segment, but not vice versa. For example, a program executing from the Secure Segment can flow into the General Segment but not into the Boot Segment.

Program Flow Change (PFC) occurs when the Program Counter is reloaded as a result of Call, Jump, Computed Jump, Return, Return from Subroutine, or other form of branch instruction. A PFC allows the program flow to follow an alternate path. A normal PFC only allows the program to branch within the same segment. A Restricted PFC allows the program to branch to a special Segment Access Area of a higher security segment.

Vector Flow Change (VFC) occurs when the Program Counter is reloaded with an Interrupt or Trap vector.

Jumping into secure code at unintended locations can expose code to algorithm detection. Therefore, PFC and VFC operations are restricted if they violate the privilege hierarchy.

Figure 23-8: Program Flow Rules

Table 23-18 presents an overview matrix of possible operations between program memory segments. Blank cells indicate conditions where read/write/erase and PFC operations can not be performed. When the Boot Segment or Secure Segment is implemented with high security level, a PFC from a lower privilege level must be restricted to the segment access area. Any PFC attempt outside the segment access area results in a security Reset (refer to **Section 23.11.3** "**Program Flow Errors**").

Table 23-18: Possible Operations Between Program Memory Segments

|                           |          | Operation To: |                    |                      |           |                                |           |           |  |  |  |  |  |  |

|---------------------------|----------|---------------|--------------------|----------------------|-----------|--------------------------------|-----------|-----------|--|--|--|--|--|--|

| Code<br>Executed<br>From: |          |               | egment<br>ty Level | Secure S<br>Security | •         | General Segment Security Level |           |           |  |  |  |  |  |  |

|                           |          | Standard      | High               | Standard             | High      | Standard                       | High      | None      |  |  |  |  |  |  |

| BS                        | Standard | R, P, PFC     |                    | R, P, PFC            | PFC*      | R, P, PFC                      | PFC       | R, P, PFC |  |  |  |  |  |  |

| 82                        | High     |               | R, P, PFC          | R, P, PFC            | PFC*      | R, P, PFC                      | PFC       | R, P, PFC |  |  |  |  |  |  |

| SS                        | Standard | PFC           | PFC*               | R, P, PFC            |           | R, P, PFC                      | PFC       | R, P, PFC |  |  |  |  |  |  |

| 33                        | High     | PFC           | PFC*               |                      | R, P, PFC | R, P, PFC                      | PFC       | R, P, PFC |  |  |  |  |  |  |

|                           | Standard | PFC           | PFC*               | PFC                  | PFC*      | R, P, PFC                      |           |           |  |  |  |  |  |  |

| GS                        | High     | PFC           | PFC*               | PFC                  | PFC*      |                                | R, P, PFC |           |  |  |  |  |  |  |

|                           | None     | PFC           | PFC*               | PFC                  | PFC*      |                                |           | R, P, PFC |  |  |  |  |  |  |

Legend: R - Read

P - Program (write)/Erase

PFC - Program Flow Change allowed to anywhere in the segment

PFC\* - Restricted Program Flow changes (can branch to Segment Access areas only)

## 23.11.1 Flow Changes